Story

June 27, 2022

Excessive-precision analog-to-digital converters (ADCs) are an integral a part of many satellites and different techniques utilized in area. You will need to perceive how such units reply within the harsh setting of area, the place heavy ions might repeatedly strike. A detection algorithm can adequately establish single-event results (SEE) – specifically, single-event transients (SET) and single-event purposeful interrupts (SEFI) – in low-speed precision SAR [successive approximation register] ADCs with out user-configurable registers. This data can be utilized to adequately decide the suitability of an ADC for area functions.

Using a detection algorithm to guage how a high-precision analog-to-digital converter (ADC) will fare in area locations the ADC right into a set of real-world working situations to check the machine in a way in keeping with its precise utilization. Making use of this methodology requires that the ADC operates with an analog enter in the course of its enter voltage vary. This format allows detection of transient occasions in each the optimistic and detrimental instructions. Working the machine in the course of its enter voltage vary is in keeping with regular operation of the half in a real-world software, since most functions require most enter sign vary.

Commentary of the ADC digital output codes might be carried out by a logic analyzer or an FPGA [field-programmable gate array]. The examples offered right here give attention to the execution of this methodology utilizing a logic analyzer. The strategy is designed to detect any occasion the place the digital output code(s) is/are past a specified threshold. Relying upon the size of such an occasion, it may be decided if these occasions are SET or SEFI [single-event transients or single-event functional interrupts]. The edge used for occasion detection is device-specific and relies upon a variety of components. A few of these components embody decision and inherent ADC noise in addition to environmental noise components. A calibration run should be carried out on the SEE testing facility previous to making use of radiation to find out the anticipated code and the suitable detection threshold vary.

At a minimal, SEE testing must be carried out utilizing a minimum of 4 heavy ions throughout a variety of LET [linear energy transfer] values from 1 to 86 MeV•cm2/mg. Testing with a minimum of 4 heavy ions offers sufficient information factors to generate an appropriate Weibull match curve (to indicate chance). On the lowest LET worth the place no SEEs are noticed, there isn’t any want to check at any decrease LET values.

The strategy right here can have a number of implementations. The first focus right here is on using a logic analyzer however the detection algorithm can be carried out in an FPGA. The output information from the ADC is enter to a logic analyzer in parallel format. Since most low-speed precision SAR ADCs use a SPI [serial peripheral interface] bus for information output, every information bit should be collected and put collectively to type the pattern phrase. An on-board advanced programmable logic machine (CPLD) or comparable logic machine can present the conversion begin sign and serial information clock to the ADC in addition to carry out the serial-to-parallel conversion.

What’s used to check?

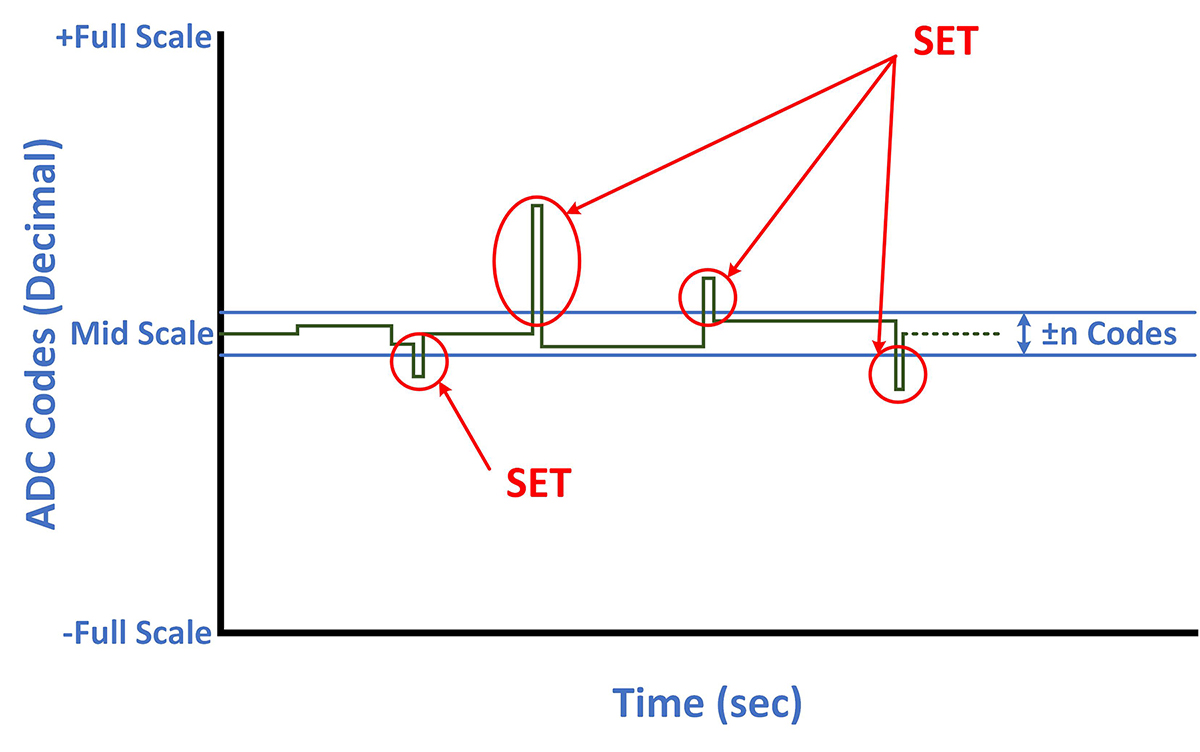

Logic analyzers provide from one to 4 parallel port enter buses, which is adequate for many check circumstances. A 14-bit precision SAR ADC and the Keysight 16861A logic analyzer is used on this instance. This logic analyzer affords two 16-bit parallel bus inputs every with a clock enter. The logic analyzer is ready as much as detect code deviations (SET) outdoors a specified window on a per pattern foundation. This SET detection algorithm identifies single pattern transients in addition to consecutive pattern transients. Determine 1 reveals the complete output code vary for an ADC with an instance plot of output codes in inexperienced and an instance SET threshold in blue. Instance transient occasions are highlighted in pink. (Determine 1.)

[Figure 1 | Pictured: a single-event transient (SET) detection window.]

The logic analyzer software program is ready to routinely report the time when an SET occasion is detected. Extra separate software program is required to carry out post-processing of the info to find out the quantity and magnitude of single and a number of pattern occasions primarily based on the recorded information and occasions.

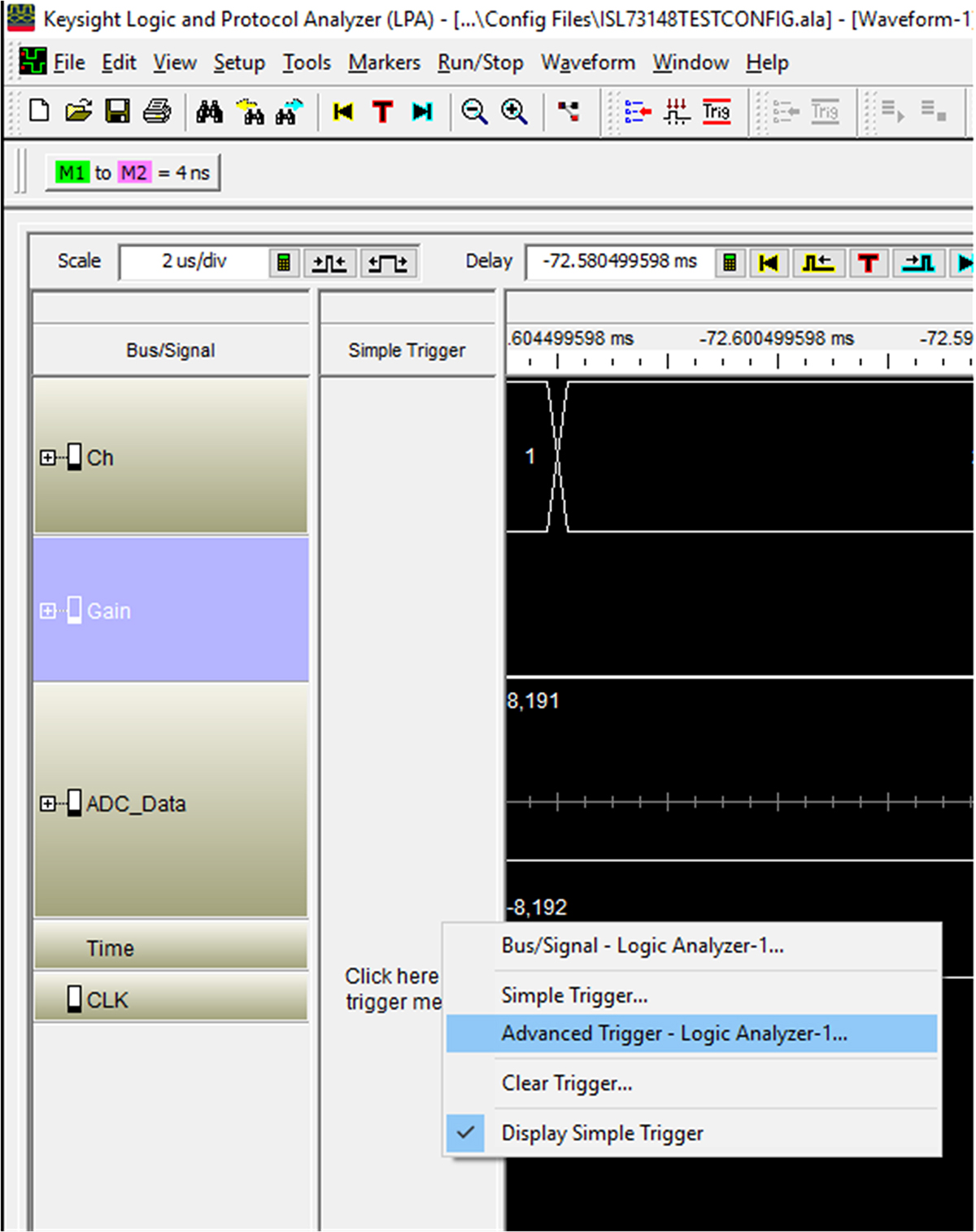

Previous to any SET run, every machine must be noticed with no radiation utilized to search out the suitable SET window. The window must be set such that it’s simply above the inherent noise stage of the ADC and any noise from the check setting. Within the following examples, the window is ready to ±8 codes centered on the common midscale code of 8200. Setting the ADC enter to a mid-scale code allows transient excursions to be noticed in each optimistic and detrimental instructions. To arrange the logic analyzer appropriately the superior set off function of the Keysight 168161 logic analyzer is utilized and might be accessed as proven in Determine 2.

[Figure 2 | Pictured: the advanced trigger feature of a Keysight logic analyzer.]

Choosing the superior set off menu

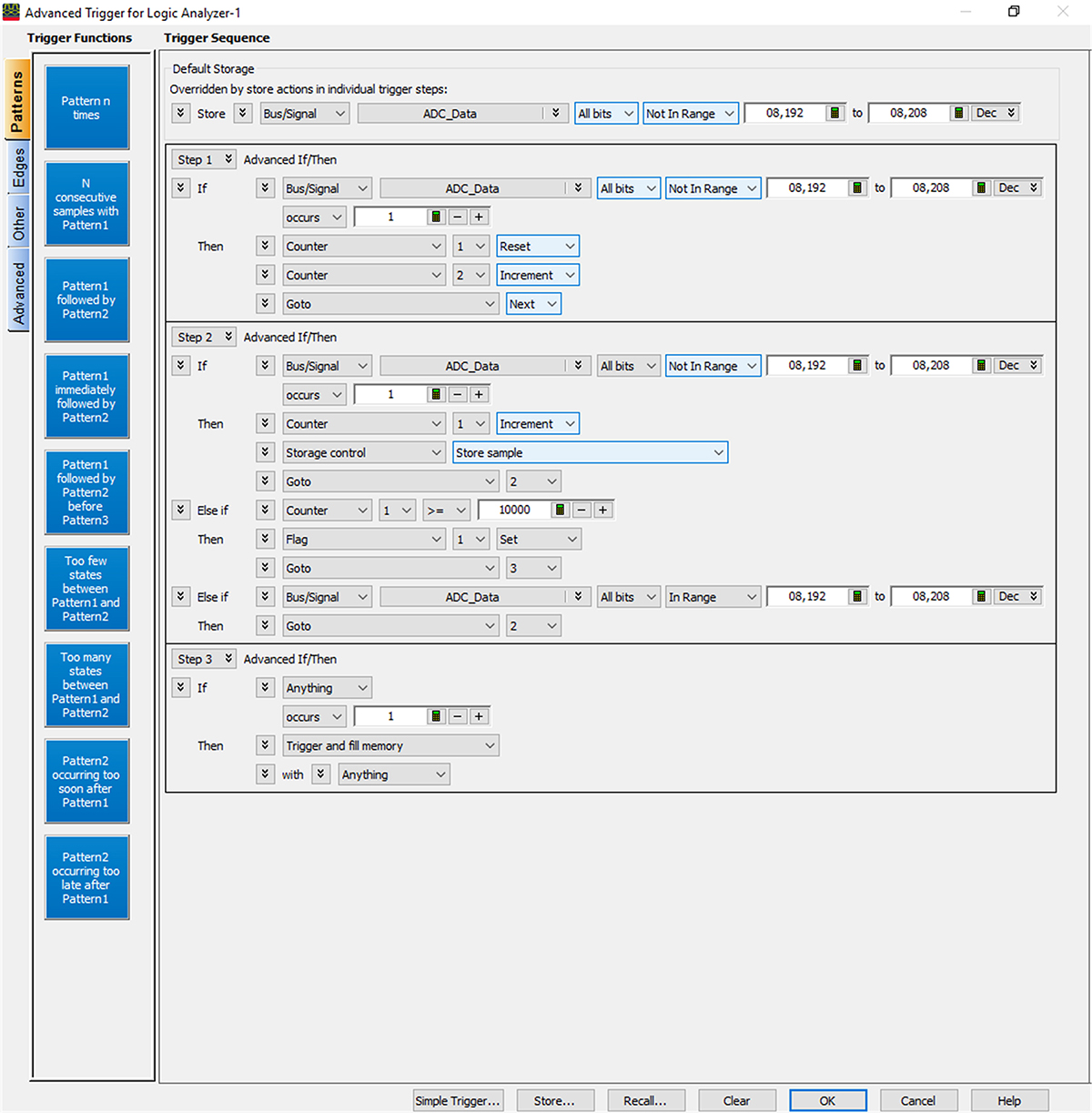

You will need to notice that every step quantity within the superior set off operation corresponds to at least one enter clock cycle. This limits processing of the pattern to easy detection within the logic analyzer, however exterior software program is used to course of the info as talked about beforehand. The superior set off menu is ready up within the detection window. When a pattern is inside this specified vary, the logic analyzer doesn’t retailer the pattern. A counter operate is used that may be programmed to the specified most variety of SET. (Determine 3.)

[Figure 3 | Pictured: the advanced trigger menu setup on the Keysight 16861A logic analyzer.]

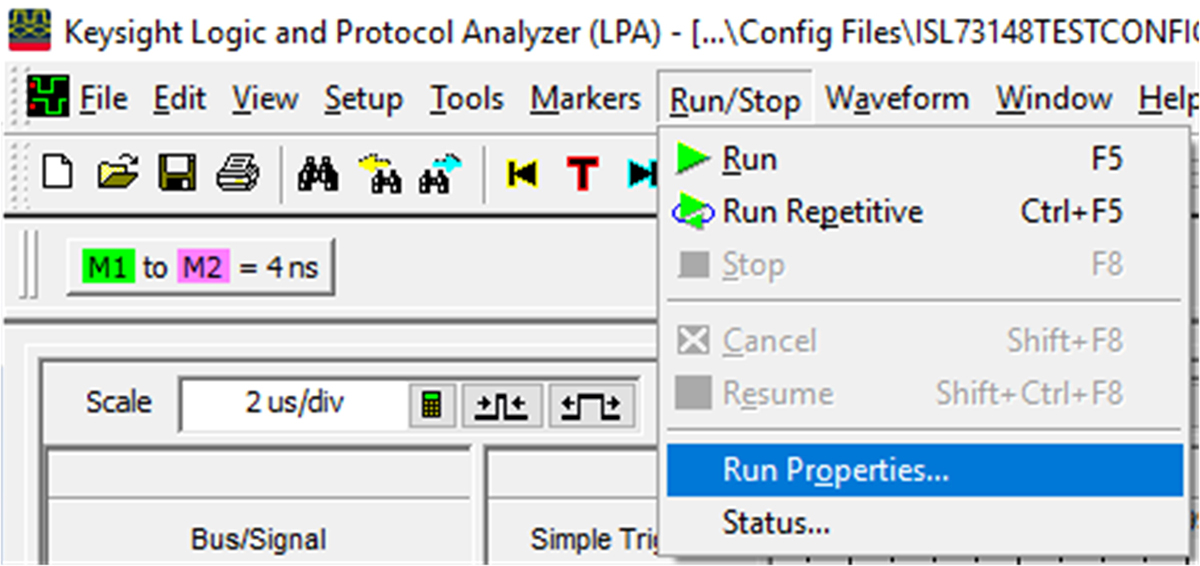

At any level throughout the operation of the check, the execution of the algorithm within the logic analyzer might be stopped and at this level the saved samples are saved to a file; that’s, if the utmost fluence has been reached however the most depend has not been reached. This step is completed by clicking “cease” underneath the run/cease menu. (Determine 4.)

[Figure 4 | Pictured: the run/stop menu selection.]

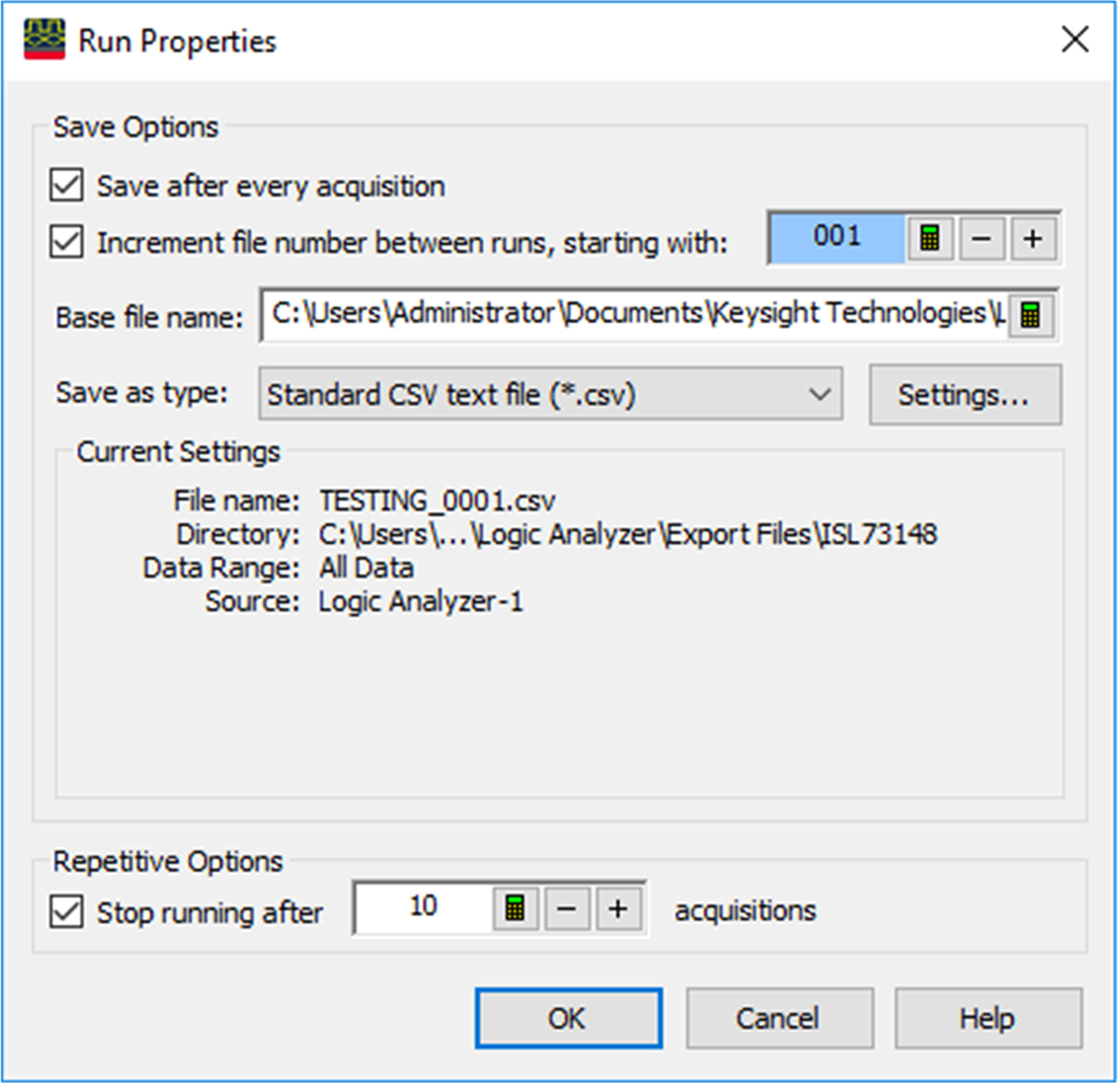

The logic analyzer should be configured to seize the suitable information and reserve it right into a identified location. That is chosen underneath the run/cease menu as proven in Determine 5. From the run/cease menu the run properties choice is chosen to specify what’s captured when the superior set off detects a pattern outdoors the required threshold. On this window the logic analyzer is specified to avoid wasting after each acquisition, to increment the file title between runs, and to cease working after 10 acquisitions (this cease is generally only a precaution since just one acquisition is important). As well as, the file location and file sort for the info is specified. The info recorded contains all the info within the waveform together with samples that violate the brink together with the time stamps of every information level. Saving the time stamp together with the info offers the size of every SET. This step allows identification of single- and multiple-sample occasions through the use of software program to calculate the time delta between time stamps to search out the variety of pattern durations between recorded SET occasions. (Determine 5.)

[Figure 5 | Pictured: the run properties menu selection.]

A SEFI occasion might be recognized if the counter reaches its most. Within the occasion this happens, then a secondary learn of the ADC output code is carried out utilizing a regular information seize within the logic analyzer. If the ADC output code stays at a worth outdoors of the anticipated window, then a SEFI might have occurred. As soon as this situation is recognized a reset of the machine if obtainable must be carried out. Upon resetting, one other commonplace information seize is carried out to see if the situation has remedied. If not, an influence cycle must be carried out adopted by one other commonplace information seize. If the ADC output code nonetheless doesn’t return to the anticipated vary, then the ADC might have everlasting harm.

What this testing accomplishes

This check methodology offers detection of SET and SEFI for precision SAR ADCs, which implies that single-sample transient occasions, multiple-sample transient occasions, and SEFI might be recognized. This check methodology workouts and observes the complete vary of the ADC to imitate the expertise of an actual software. The outcomes of testing with this methodology allow the SEE efficiency of the ADC to be projected in an software by plotting the Weibull match curves for the saturation cross part and utilizing the CRÈME96 mannequin for the suitable orbit.

Jonathan Harris is an functions engineer within the area and hi-rel merchandise group at Renesas in Palm Bay, Florida. He has over 15 years of functions expertise with greater than 10 of these years supporting ADC merchandise. He enjoys a great sport of desk tennis, tinkering with automotive audio, and using bikes. He might be reached at [email protected].

Renesas

Featured Firms

Renesas

Milpitas, CA 95035